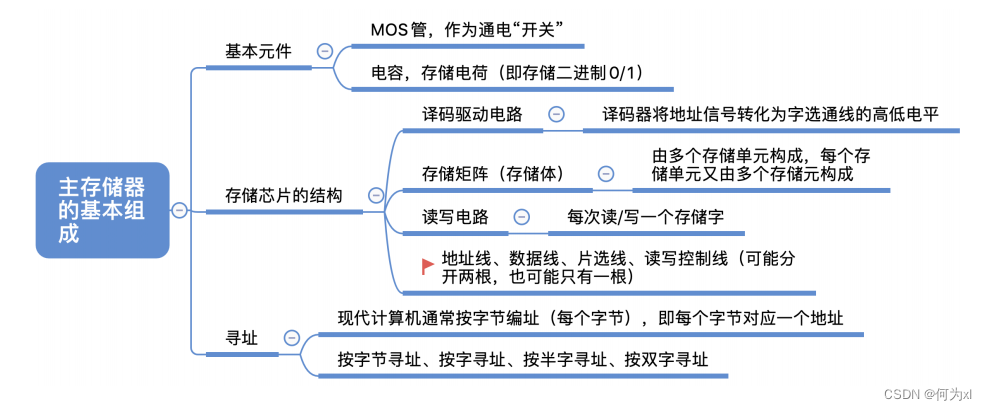

一、主存储器的基本组成

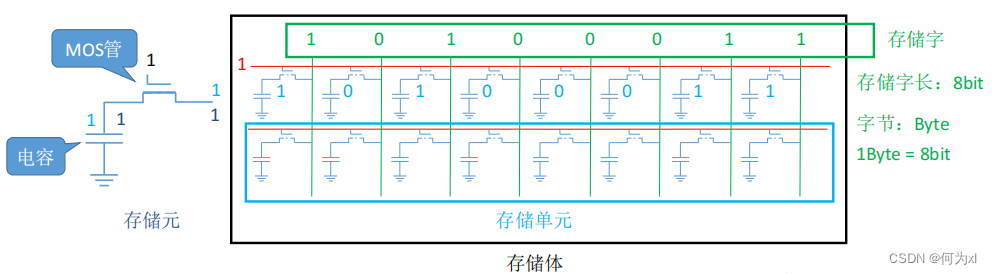

(一)、基本的半导体元件

注:MOS管可理解为一种电控开关,输入电压达到某个阈值时,MOS管就可以接通。

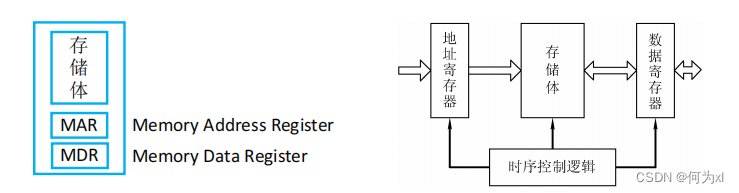

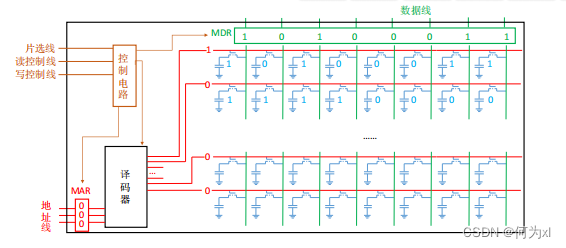

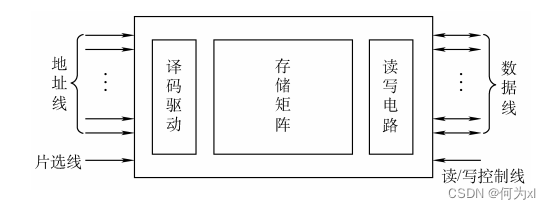

(二)、存储器芯片的基本原理

(三)、总结

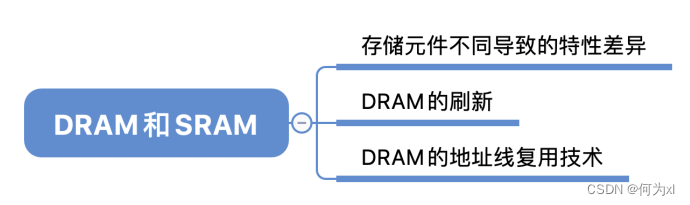

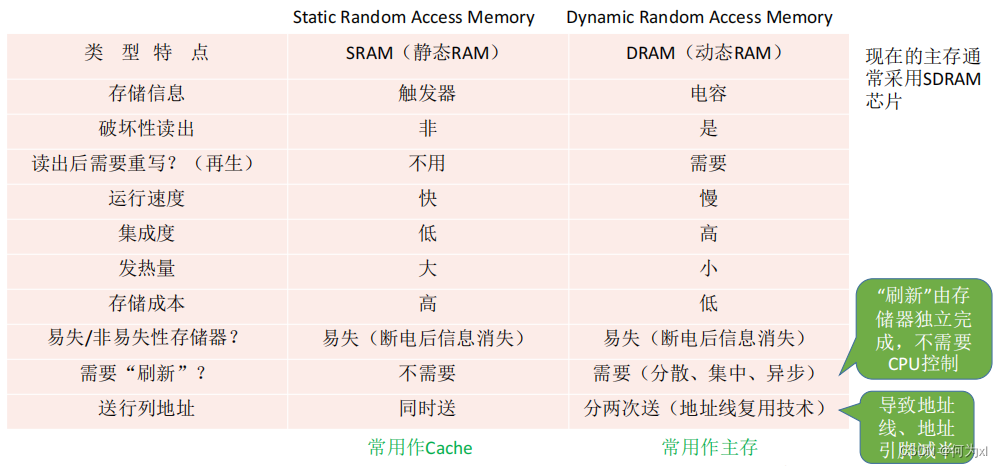

二、SRAM 和 DRAM

1 动态RAM(Dynamic Random Access Memory)DRAM

2 静态RAM(Static Random Access Memory)SRAM

DRAM用于主存、SRAM用于Cache

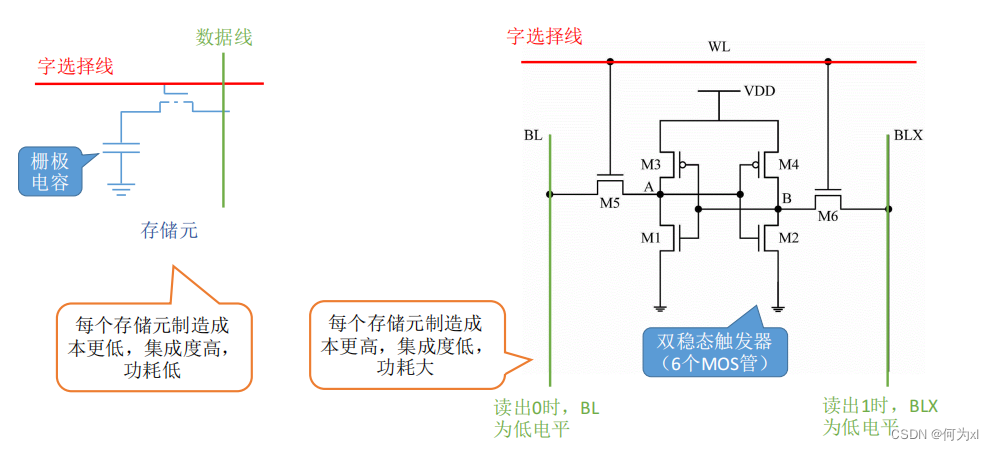

(一)、栅极电容 V.S. 双稳态触发器

DRAM芯片:使用栅极电容存储信息

SRAM芯片:使用双稳态触发器存储信息

核心区别:存储元不一样

可以看到双稳态触发器使用 6个MOS管,栅极电容使用一个 MOS 管,故 SRAM 与 DRAM 的一些特性可以由此得到。

栅极电容:电容内的电荷只能维持2ms。即便不断电,2ms后信息也会消失。2ms之内必须“刷新”一次(给电容充电)。

双稳态触发器:只要不断电,触发器的状态就不会改变。

(二)、DRAM 的刷新

多久需要刷新一次? 刷新周期:一般为2ms。

每次刷新多少存储单元?以行为单位,每次刷新一行存储单元。

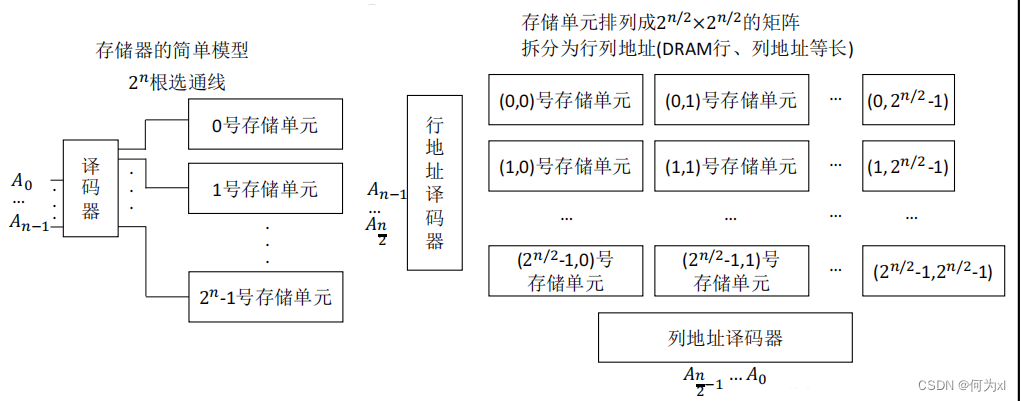

注:DRAM 使用行列地址,可以减少选通线的数量。

假设DRAM内部结构排列成128×128 的形式,读/写周期0.5us ,2ms 共 2ms/0.5us = 4000 个周期

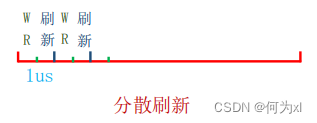

1. 分散刷新

思路一:每次读写完都刷新一行。

方式:系统的存取周期变为1us,前0.5us时间用于正常读写

后0.5us时间用于刷新某行。

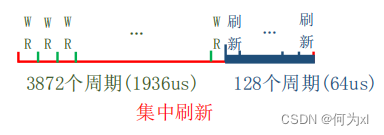

2. 集中刷新

思路二:2ms 内集中安排时间全部刷新。

方式:系统的存取周期还是0.5us,有一段时间专门用于刷新,无法访问存储器,称为访存“死区”。

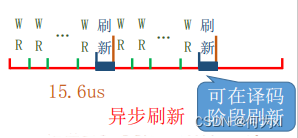

3. 异步刷新

思路三:2ms内每行刷新1次即可 。

方式:2ms内需要产生128次刷新请求每隔 2ms/128 = 15.6us 一次,每15.6us内有0.5us的“死时间”。

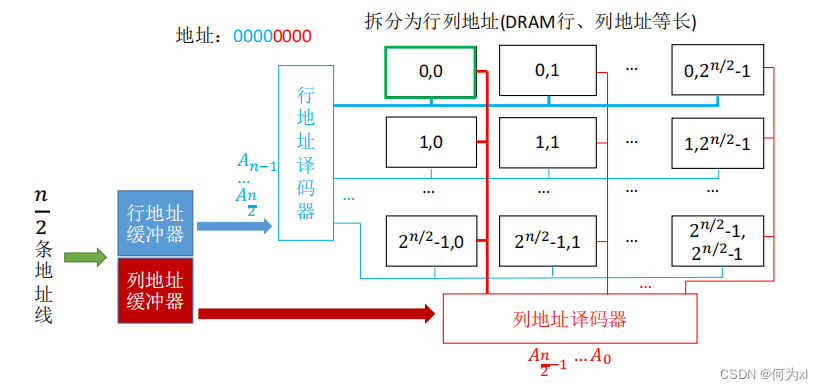

(三)、DRAM 的行列地址划分

(四)、DRAM 的地址线复用技术

行、列地址分两次送,可使地址线更少,芯片引脚更少。

(五)、DRAM 与 SRAM 比较

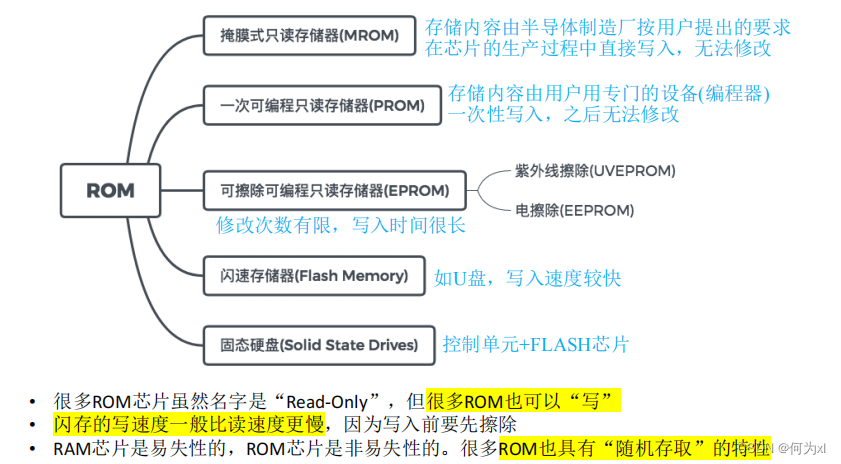

三、只读存储器(ROM)

逻辑上,主存由 RAM+ROM 组成,且二者常统一编址

RAM芯片 —— 易失性,断电后数据消失。

ROM芯片 —— 非易失性,断电后数据不会丢失。很多ROM也具有“随机存取”的特性。

(一)、ROM 的种类

任何人不可重写(只能读出)

写一次之后就不可更改

可进行多次重写

可用“电擦除”的方式,擦除特定的字。

在EEPROM 基础上发展而来,断电后也能保存信息,且可进行多次快速擦除重写。

由控制单元+存储单元(Flash 芯片)构成,与闪速存储器的核心区别在于控制单元不一样,但存储介质都类似,可进行多次快速擦除重写。

(二)、ROM 的总结

链接:https://blog.csdn.net/weixin_43848614/article/details/126820846

作者:何为xl